Plds PowerPoint PPT Presentations

All Time

Recommended

Programmable Logic Devices (PLDs)

| PowerPoint PPT presentation | free to view

Physical information (.pi): maps signals to pins. ... Fix all signals to fitter assigned pins (.pi). Compile again. ... Refit, fixing all pins to fitter defaults. ...

| PowerPoint PPT presentation | free to download

Unlike integrated circuit logic 74xxnn, functions can be changed. ... The Compile process generates a Programmer Object File (.pof file) ...

| PowerPoint PPT presentation | free to view

Document presentation format: On-screen Show (4:3) Other titles: Arial Times New Roman Wingdings Tahoma Default Design Introductory Training on the PLDs Grades K 1 ...

| PowerPoint PPT presentation | free to view

* Intermediate features of speech sample on this : This speaking task requires the ability to explain a story from pictures, which requires more than basic ...

| PowerPoint PPT presentation | free to download

Programming Logic Devices (PLDs) ( )

| PowerPoint PPT presentation | free to download

Actel FPGA FPGA FPGA(Field Programmable Gate Array) PLDs(Programmable Logic Devices) (register) Routing ...

| PowerPoint PPT presentation | free to view

* To continue with foundational ELPS-TELPAS training, you may wish to use the PowerPoint modules titled Introductory Training on the PLDs, Grades 2 12 or ...

| PowerPoint PPT presentation | free to download

Finite discrete sequence spectrum convoluted with rectangular window spectrum. ... Radix-2. DFT. N. DSPs & PLDs influenced algorithms design. ...

| PowerPoint PPT presentation | free to view

CSCE 211 Digital Design. Overview. Last Time. GALs. Sequential PLDs ... Old Exam Handout. Review (aka excuse for pizza)? ROM Varieties revisited ...

| PowerPoint PPT presentation | free to view

PROMs and EPROMs can also be used as PLDs. PROM. Used mainly as a memory device ... FPGA is reconfigured from the PROM when power is applied ...

| PowerPoint PPT presentation | free to view

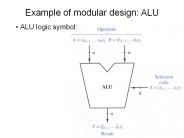

4 types PLDs: ROM, PLA, PAL, CPLD, FPGA. 1. control connection ... Example 6-3 Implementing a combinational circuit using a PAL. W(A, B, C, D) = m(2, 12, 13) ...

| PowerPoint PPT presentation | free to view

... of bits which represents the burn-in configuration of the Hardware Block (HB) eg. ... PLDs are soft wired for re-use of static hardware resources. Cost effective ...

| PowerPoint PPT presentation | free to view

See http://www.altera.com/literature/ds/m7000a.pdf. Spring 2003. 34 ... ROMs. EEPROMs. Programmable Devices. Small: PALs PLAs. Larger: PLDs, FPGAs. Spring 2003 ...

| PowerPoint PPT presentation | free to view

Programmable Logic So far, have only talked about PALs (see 22V10 figure next page). What is the next step in the evolution of PLDs? More gates! How do we get more gates?

| PowerPoint PPT presentation | free to view

HDL Languages popularly used to program FPGAs/CPLDs are VHDL and Verilog. ... Spectrum: Synthesis environment to create PLDs, FPGAs and ASICs in VHDL or Verilog. ...

| PowerPoint PPT presentation | free to view

using LabVIEW software by National Instruments or custom ... Custom interfaces. Digital Design. Digital Design using Complex PLDs ...

| PowerPoint PPT presentation | free to view

Title: Flip-Flops and Related Devices Author: whliao Last modified by: whliao Created Date: 3/28/2001 1:58:38 AM Document presentation format: (4:3)

| PowerPoint PPT presentation | free to view

- Programmable Array Logic (PAL) - Generic Array Logic (GAL) Tocci Chapter 11 (Memory Devices) Read section 11-10 Review questions of section 11-10

| PowerPoint PPT presentation | free to download

Title: The GAL16V8 PLD Author: haskell Last modified by: rehask Created Date: 4/24/2000 3:36:42 PM Document presentation format: On-screen Show Company

| PowerPoint PPT presentation | free to download

- Programmable Array Logic (PAL) - Generic Array Logic (GAL) Tocci Chapter 11 (Memory Devices) Read section 11-10 Review questions of section 11-10

| PowerPoint PPT presentation | free to download

OHE vs FSM Grafcet et FSM : restriction Si le grafcet comporte des tapes activ es en parall le, l impl mentation FSM n est pas applicable.

| PowerPoint PPT presentation | free to download

Gate array design Use a sea of basic transistors (pmos/nmos) or gates (NAND/NOR) Can have cells which can provide a universal logic function

| PowerPoint PPT presentation | free to download

fpga altera max+plus ii tool ...

| PowerPoint PPT presentation | free to download

Fabrication delay weeks or months. Pre-designed gate arrays ... Fabrication delay is hours or days. IC design methodologies. Programmable logic devices ...

| PowerPoint PPT presentation | free to download

Digital Design 1 Lecture 12 Amirali Baniasadi amirali@ece.uvic.ca * Memory Memory unit: Stores binary information A collection of cells Two types of memory: RAM ...

| PowerPoint PPT presentation | free to download

CENG 241 Digital Design 1 Lecture 13 Amirali Baniasadi amirali@ece.uvic.ca

| PowerPoint PPT presentation | free to download

Electronic Design Automation EDA

| PowerPoint PPT presentation | free to download

Circuit Board interfaced with other devices (sensors, actuators) to provide system function ... Analog interfaces. ADC, DAC, UART. Complex Electronic Hardware ...

| PowerPoint PPT presentation | free to view

Programming a Hyper-Programmable Architectures for Networked Systems Eric Keller and Gordon Brebner Xilinx Research Labs, USA Hyper-Programmable Architectures for ...

| PowerPoint PPT presentation | free to download

Servomecanismo N7SRV Prof. Dr. Cesar da Costa 6.a Aula: Controladores Baseado em FPGA Aten o: Para obter o software Quartus II, Ver. 9.1, Web Edition, site do ...

| PowerPoint PPT presentation | free to view

Electronic aspect of digital design. Digital abstraction. Range. Noise margin. Invalid range ... But: modern design, software tools are essential. Examples: ...

| PowerPoint PPT presentation | free to view

Digital cameras, MP3 players, BIOS. Limited life. Some support individual word write, some block ... of the PAL was the generic array logic device, or GAL, ...

| PowerPoint PPT presentation | free to download

Hybrid Electric Vehicles (HEVs) use batteries as a source of power for the ... The overcharging of batteries will be prevented by monitoring temperature and ...

| PowerPoint PPT presentation | free to download

CHAPTER 5 Microelectronic Design Technology

| PowerPoint PPT presentation | free to download

Lab Introduction. List of Lab Assignments. Lab Notebook Guidelines ... Introduction to Basic Gates (AND, OR, XOR) With Quartus Software ...

| PowerPoint PPT presentation | free to download

Programmable Logic Devices by Abdulqadir Alaqeeli 1/27/98

| PowerPoint PPT presentation | free to view

Hardware Compilation is bringing software compiler concepts to the design flow ... Is using a software language a feasible entry point for hardware design? ...

| PowerPoint PPT presentation | free to view

Output Inversion Ctrl. Tristate Buffer. I/O pin. Input pin. Input ... FPGAs are based on Look-up Tables (LUTs) A LUT is simply a representation of a truth table ...

| PowerPoint PPT presentation | free to view

... significant cognitive disabilities, ... of students with significant cognitive disabilities in the grade-level content ... Align with state content standards ...

| PowerPoint PPT presentation | free to view

F0 = A B'C', F1 = B'C' AB, F2 = AC' AB, And F3 = B'C A ... CS 3402--Digital Logic. Programmable Logic Device. 24. Exercises. p.380 5.1, 5.2, 5.3 ...

| PowerPoint PPT presentation | free to download

COE-202 Term - 053 Dr Abdelhafid Bouhraoua Instructor Dr Abdelhafid Bouhraoua Office Hours: Sat. Mon. Wed. 9:30 AM 11:30 PM Office Location: Bldg 22 Room 137-1 ...

| PowerPoint PPT presentation | free to download

PAL = Prog. Array of Logic. CPLD = Complex PLD. FPGA = Field Prog. Gate ... Architecture PAL/22V10-like Gate array-like. More Combinational More Registers RAM ...

| PowerPoint PPT presentation | free to download

cause SHARC sounds cool! TigerSHARC. SHARC ! DSPs - TMS320C6200. DSPs ... Dr. Greenwood has the whole FPGA lab with programming tools and interfaces as well. ...

| PowerPoint PPT presentation | free to download

November 21, 2001, Tampere, Finland Reiner Hartenstein University of Kaiserslautern Enabling Technologies for Reconfigurable Computing Part 4: FPGAs: recent developments

| PowerPoint PPT presentation | free to download

This course of lectures deals with the technology and programming of programmable logic devices ... The link map must be downloaded from an external source on power-up ...

| PowerPoint PPT presentation | free to view

Universidad de Oviedo Departamento de Inform tica Tesis Doctoral Modelo de Cobertura en Redes Inal mbricas basada en Radiosidad por Refinamiento Progresivo

| PowerPoint PPT presentation | free to download

Title: Lesson 1 Author: Lucien Last modified by: Dept, Electrical & Computer Engineering Created Date: 9/11/2005 1:04:05 PM Document presentation format

| PowerPoint PPT presentation | free to view

PAL with 4 inputs, 4 outputs, and 3-wide AND_OR Structure. Implement the following functions with a PAL: ... Fuse Map for PAL. SEQUENTIAL PROGRAMMABLE DEVICES ...

| PowerPoint PPT presentation | free to view

TDC Mezzanine Card (XTC) ... The mezzanine card is responsible. for classifying each hit on a wire. as either ... Input to Mezzanine: 16138 axial wires ...

| PowerPoint PPT presentation | free to download

Supplied with no predetermined logic function ... Easy to learn for beginner. A few data types. Hardware related. Wires. Registers ...

| PowerPoint PPT presentation | free to view

Telling Your Story With Numbers. Annual Northwest Resource Sharing and ... Blogs. Juice Analytics http://www.juiceanalytics.com/weblog ...

| PowerPoint PPT presentation | free to view

... technologies from Full Custom to FPGAs increases for a fixed-sized design. ... Used in ASIC as well as custom design environment ...

| PowerPoint PPT presentation | free to download

Zaburzenia psychiczne wyst puj ce w przebiegu boreliozy Lek. Jan Karol Cichecki Problem ... x 10? Historia bada nad borelioz Afzelius ...

| PowerPoint PPT presentation | free to view

Lecture 12 Digital Circuit Implementation Issues PLAs, PALs, ROM s, FPGA s Packaging Issues Look Up Table method Multiplexer Method

| PowerPoint PPT presentation | free to download

Separate inventories for K and grades 1-2. Listening, Speaking, ... 3 possible score ... Finally, students can compose narrative and some descriptive ...

| PowerPoint PPT presentation | free to view