New Verilog-A capability available in Agilent simulators PowerPoint PPT Presentation

Title: New Verilog-A capability available in Agilent simulators

1

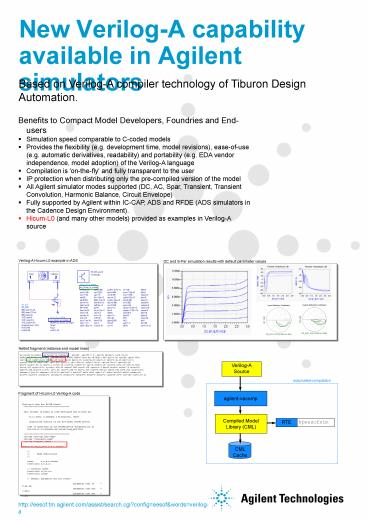

- New Verilog-A capability available in Agilent

simulators

Based on Verilog-A compiler technology of Tiburon

Design Automation.

- Benefits to Compact Model Developers, Foundries

and End-users - Simulation speed comparable to C-coded models

- Provides the flexibility (e.g. development time,

model revisions), ease-of-use (e.g. automatic

derivatives, readability) and portability (e.g.

EDA vendor independence, model adoption) of the

Verilog-A language - Compilation is 'on-the-fly' and fully transparent

to the user - IP protection when distributing only the

pre-compiled version of the model - All Agilent simulator modes supported (DC, AC,

Spar, Transient, Transient Convolution, Harmonic

Balance, Circuit Envelope) - Fully supported by Agilent within IC-CAP, ADS and

RFDE (ADS simulators in the Cadence Design

Environment). - Hicum-L0 (and many other models) provided as

examples in Verilog-A source

Verilog-A Hicum-L0 example in ADS

DC and S-Par simulation results with default

parameter values

Netlist fragment (instance and model lines)

my_hicum_va_model my_hicum_va_instance _net249

_net250 0 0 _net251 Noise1 is8.7e-18 model

my_hicum_va_model hicum_l0_va NPN1 PNP0

is8.4e-18 mcf1.045 mcr1.05 vef80 iqf0.055\

iqr1e10 iqfh1e10 tfh1e-08 ibes3e-20

mbe1.01 ires6e-15 mre2.9 ibcs7.4e-18

mbc1.13\ cje01.63e-14 vde0.895 ze0.525

aje1.5 t01.45e-12 dt0h7.5e-13 tbvl9.5e-13

tef05e-14\ gte6 thcs2.5e-11 ahc0.1

tr1e-10 rci030 vlim0.36 vpt4 vces0.18

cjci01.017e-14 vdci0.694\ zci0.393 vptci4.22

cjcx01.67e-15 vdcx0.588 zcx0.328 vptcx1.4

fbc0 rbi06 vr0e7.4 vr0c26\ fgeo0.656 rbx25

rcx11 re1.85 iscs7.28e-16 msc1.035

cjs08.79e-15 vds0.348 zs0.306 vpts4.44\

cbcpar3.25e-15 cbepar1.327e-14 eavl26.3

kavl57 kf0 af2 vgb1.17 alb0 alt00 kt00

zetaci0\ alvs0 alces0 zetarbi0 zetarbx0

zetarcx0 zetare0 alkav0 aleav0 tnom20 dt0

rth100 cth0.1e-12

Fragment of Hicum-L0 Verilog-A code

Verilog-A code for HICUM Level0

This

release is based on code developed and written

by 23.11.2002 S.Lehmann M.Schroter,

CEDIC (simplified version of the BJT

model HICUM Level2) Code is described in

the HICUM/Level0 documentation at

www.iee.et.tu-dresden.de/iee/eb/comp_mod.html

include

"disciplines.vams" include "constants.vams" inc

lude "compact.vams" module hicum_l0_va(c,b,e,s,tn

ode) // // Node definitions

// inout c,b,e,s,tnode electrical

c,b,e,s // internal nodes electrical

ci,bi,ei electrical tnode // default

parameter set for level0 parameter real is

8.4e-18 parameter real mcf

1.045 parameter real mcr 1.05

http//eesof.tm.agilent.com/assist/search.cgi?conf

igeesofwordsverilog-a