Ingen lysbildetittel - PowerPoint PPT Presentation

1 / 26

Title:

Ingen lysbildetittel

Description:

... (addr, rdy, ref, read, burst, present_state) begin. case present_state ... if (rdy and not burst) = '1' then. next_state = s0; elsif (rdy and burst) = '1' then ... – PowerPoint PPT presentation

Number of Views:26

Avg rating:3.0/5.0

Title: Ingen lysbildetittel

1

(No Transcript)

2

(No Transcript)

3

(No Transcript)

4

(No Transcript)

5

(No Transcript)

6

(No Transcript)

7

(No Transcript)

8

library ieee use ieee.std_logic_1164.all entity

machine is port( clk, rst in

std_logic addr, cnt in std_logic_vector(15

downto 0) ads,rdy, ref, read, burst in

std_logic set buffer std_logic_vector(4

downto 0)) end machine architecture machine of

machine is type states is (s0, s1, s20, s21,

s22, s23, s24, s30, s31, s32, s33, s34, s35,

s36, s37, s40, s41) attribute state_encoding of

statestype is one_hot_one signal

present_state, next_state states begin p1

process (addr, rdy, ref, read, burst,

present_state) begin case present_state

is . end case end process

9

case present_state is when s0 gt if addr

"1010101010101010" and ads '1'

then next_state lt s1 end if when

s1 gt if ref '1' then next_state lt

s40 elsif (rdy and not ref and read) '1'

then next_state lt s30 elsif (rdy and

not ref and not read) '1' then next_state

lt s20 end if when s20 gt next_state

lt s21 when s21 gt if (rdy and not burst)

'1' then next_state lt s0 elsif (rdy

and burst) '1' then next_state lt

s22 end if when s22 gt next_state lt

s23 when s23 gt next_state lt s24 when

s24 gt if rdy '1' then next_state lt

s0 end if when s30 gt next_state lt

s31

10

when s30 gt next_state lt s31 when s31

gt if (rdy and not burst) '1' then

next_state lt s0 elsif (rdy and burst)

'1' then next_state lt s32 end

if when s32 gt next_state lt s33 when s33

gt if rdy '1' then next_state lt

s34 end if when s34 gt next_state lt

s35 when s35 gt if rdy '1' then

next_state lt s36 end if when

s36 gt next_state lt s37 when s37 gt if

rdy '1' then next_state lt s0 end

if when s40 gt next_state lt s41 when s41

gt if cnt "1111111100000001"

then next_state lt s0 end if end

case

11

p2 process (clk, rst) begin if rst '1'

then present_state lt s0 elsif clk'event

and clk '1' then present_state lt

next_state end if end process p3 process

(present_state) begin set lt "00000" case

present_state is when s0 gt set(0) lt

'1' when s1 gt set(1) lt '1' when s20

s21 s22 s23 s24 gt set(2) lt

'1' when s30 s31 s32 s33 s34 s35

s36 s37 gt set(3) lt '1' when s40 s41

gt set(4) lt '1' end case end

process end

12

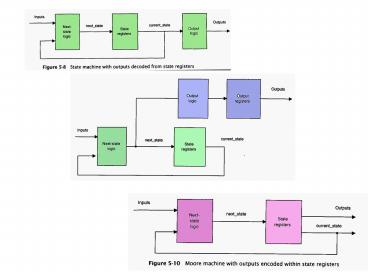

Moore og Mealy tilstandsmaskiner

13

library ieee use ieee.std_logic_1164.all entity

mealy1 is port( clk, rst in std_logic id in

std_logic_vector(3 downto 0) w out

std_logic y out std_logic_vector(1 downto

0)) end mealy1 architecture archmealy1 of

mealy1 is type states is (state0, state1,

state2, state3, state4) signal state

states begin moore process (clk, rst)

begin if rst'1' then state lt

state0 elsif (clk'event and clk'1')

then case state is when state0 gt if

id x"3" then state lt state1 else

state lt state0 end if when state1

gt state lt state2

14

when state2 gt if id x"7"

then state lt state3 else state

lt state2 end if when state3

gt if id lt x"7" then state lt

state0 elsif id x"9" then state lt

state4 else state lt state3 end

if when state4 gt if id x"b"

then state lt state0 else state

lt state4 end if end case end

if end process --assign moore state

outputs y lt "00" when (statestate0) else

"10" when (statestate1 or statestate3) else

"11" --assign mealy output w lt '0' when

(statestate3 and id lt x"7") else '1' end

archmealy1

15

library ieee use ieee.std_logic_1164.all --

simple security system uses a mealy

machine ENTITY securitySystem IS PORT (set,

intruder, clk IN std_logic horn OUT

std_logic) END securitySystem ARCHITECTURE

behavior OF securitySystem IS TYPE states IS

(securityOff, securityOn, securityBreach) SIGNAL

state, nextState states BEGIN PROC1 PROCESS

(set, intruder) . END

PROCESS proc2 PROCESS BEGIN WAIT UNTIL

clk '1' state lt nextState END

PROCESS END behavior

16

PROC1 PROCESS (set, intruder) BEGIN CASE

state IS WHEN securityOff gt IF set '1'

THEN nextState lt securityOn ELSE next

State lt securityOff END IF WHEN

securityOn gt IF intruder '1' THEN horn

lt '1' nextState lt securityBreach ELSIF

set '0' THEN horn lt '0' nextState lt

securityOff ELSE nextState lt

securityOn END IF WHEN securityBreach

gt IF set '0' THEN horn lt

'0' nextState lt securityOff ELSE nex

tState lt securityBreach END IF WHEN

others gt nextState lt securityOff END

CASE END PROCESS

17

Tilstandsenkoding og enumeration type

18

Implisitt dont care

19

Feiltoleranse

- I sikkerhetskritiske systemer må en komme til

kjente tilstander - krever ekstra logikk

20

(No Transcript)

21

(No Transcript)

22

Eksplisitt tilstandsenkodingdont cares og

feiltoleranse

23

Feiltoleranse for one-shot maskiner

24

Ufullstendig spesifisering av IF-THEN-ELSE

25

Oppsummering

26

Eksempler Trafikklys Innbruddsalarm Innbruddsal

arm2