Example: Verification PowerPoint PPT Presentation

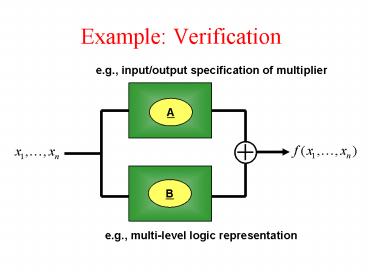

Title: Example: Verification

1

Example Verification

e.g., input/output specification of multiplier

e.g., multi-level logic representation

2

Binary Decision Diagrams

Graph-based Representation of Boolean Functions

- Introduced by Lee (1959).

- Popularized by Bryant (1986).

- compact (functions of 50 variables)

- efficient (linear time manipluation)

Widely used has had a significant impact on the

CAD industry.

3

Binary Decision Diagrams

Graph-based Representation of Boolean Functions

1

0

BDD is defined as Directed Acyclic Graph

0

0

1

1

4

Analysis of Digital Circuits

Large domain, small range.

inputs

5

Analysis of Digital Circuits

Large domain, small range.

inputs

2m possibilities

2 possibilities

6

Data Structures

Truth Tables

Example

4 rows

2 variables

8 rows

3 variables

264 rows

64 variables

7

Data Structures

Decision Diagrams

Example

x1

x2

x3

f

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

1

1

0

0

0

1

0

1

1

1

1

0

0

1

1

1

1

8

Data Structures

Decision Diagrams

Optimize by merging nodes

x3

x3

x3

x3

9

Data Structures

Decision Diagrams

S

Optimize by merging nodes

x1

1

0

x2

1

x3

x3

x3

0

1

0

1

1

10

Data Structures

Decision Diagrams

Optimize by merging nodes

x2

x2

11

Data Structures

Decision Diagrams

S

Optimize by merging nodes

x1

0

x2

1

0

x3

1

0

12

Data Structures

Logic Operations

AND

13

Decision Diagrams

Properties

- Canonical unique up to variable ordering

- Compact represent functions of up to 1000

variables - Efficient perform logic operations in

linear-time

14

Ordered Binary Decision Diagrams

(a.k.a. Branching Programs)

Example

Directed Acyclic Graph variables are inspected

in order.

15

Reducing OBDDs

Terminal Rule eliminate duplicate terminals.

16

Reducing OBDDs

Elimination Rule eliminate a node if its 0 and

1 edges lead to the same node.

17

Reducing OBDDs

Merging Rule merge two nodes that reference

the same variable and point to the same

successors.

18

Reduced OBDDs

Question

What is the optimal strategy for eliminate and

merge operations?

19

Reduced OBDDs

Strategy eliminate and merge nodes repeatedly,

in any order, until no further simplifications

are possible.

Is the result unique?

20

Uniqueness (proof)

By induction on the number of variables.

Induction Hypothesis Assume that any two ROBDDs

for a function with k 1 variables, k gt 0, are

isomorphic.

Inductive Step Show that any two ROBDDs for a

function with k variables are isomorphic.

21

Inductive Step

22

Inductive Step

Show that this mapping is well-defined and

one-to-one.

23

Inductive Step

24

Mapping Well-Defined

low(v)

high(v)

Counter Example (Unreduced BDDs)

25

Mapping One-To-One

Counter Example (Unreduced BDDs)

26

Logic Operations

27

Logic Operations

28

Logic Operations

Compute

0

1

0

1

29

Logic Operations

30

Logic Operations

31

Logic Operations

32

Logic Operations

33

Logic Operations

0

1

34

Logic Operations

0

1

35

Logic Operations

0

1

36

Logic Operations

0

1

37

Logic Operations

Simplify

0

1

38

Logic Operations

Simplify

39

Variable Ordering