Architecture Overview (Start here on Fri) PowerPoint PPT Presentation

1 / 14

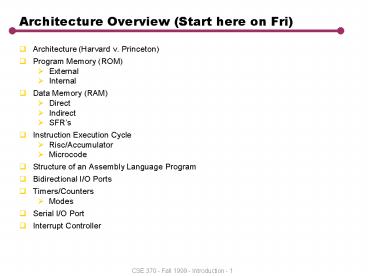

Title: Architecture Overview (Start here on Fri)

1

Architecture Overview (Start here on Fri)

- Architecture (Harvard v. Princeton)

- Program Memory (ROM)

- External

- Internal

- Data Memory (RAM)

- Direct

- Indirect

- SFRs

- Instruction Execution Cycle

- Risc/Accumulator

- Microcode

- Structure of an Assembly Language Program

- Bidirectional I/O Ports

- Timers/Counters

- Modes

- Serial I/O Port

- Interrupt Controller

2

Simple Princeton Architecture

ROM Linear Address Space W/ Mem Mapped

IO/SFRs

I/O Port

PC

SP

GPRs

IR

Timer, SFRs

RAM

address

ALU

Reset Vector

Interrupt Vect

IR

mux

data

Status

Control

3

Analysis

- Bottleneck into and out of memory for data and

code - Use of critical 8-bit address space (256) for

memory mapped I/O and special function registers

(timers and their controllers, interrupt

controllers, serial port buffers, stack pointers,

PC, etc). For example, the Motorola 6805

processor has only 187 RAM locations. - But, easy to program and debug. Compiler is

simple too.

4

8051 Modified Harvard Architecture

PC

mux

address

Internals

RAM

SFRs (direct)

Reset Vector

Usually Stack (indirect)

ALU

Interrupt Vect

Interrupt Vect

Interrupt Vect

8051 standard Enhancements

(indirect or Direct)

Bit Addressable

Status

Reg. Banks

data

Control

5

8051 Memory Architecture

- Advantages

- Simultaneous access to Program and Data store

- Register banks great for avoiding context

switching on interrupt and for code compression - 8-bit address space extended to 256128 384

registers by distinguishing between direct and

indirect addressing for upper 128 bytes. Good for

code compression - Bit addressable great for managing status flags

- Disadvantage

- A little bit confusing, with potential for

errors.

6

Instruction Execution

- 6 states/machine cycle, 2 clocks/state 12

clocks/machine cycle. Some instructions take two

machine cycles, most take one. - Can make two ROM accesses in on memory cycle?

(three byte inst) - More like CISC than RISC

- Interesting features

- No Zero flag (test accumulator instead)

- Bit operations

- Read Modify Write operations (ports)

- Register to Register Moves

- Integer arithmetic

- Signed arithmetic

- Byte and Register Exchange operations

7

Assembly Programming

- Declare Segments and Segment types

- Assembler converts to machine code, with

relocatable segments. - Linker perform absolute code location

- Segments

- DATA

- IDATA

- PDATA

- XDATA

- CODE

- CONST

- Example Assembly Program

8

Anatomy of an Assembly Program

Look for overflow in C difficult to do

unsigned int i void main (void) unsigned

int tmp while (1) P1 0x01 i 0 do

tmp i i P2 while (tmp lt i)

Note i is global and tmp is local. What happens

to local variables? How are registers used? What

happens in a subroutine call?

9

Now in Assembly

RSEG PROG first set Stack

Pointer START MOV SP,STACK-1 CLR flag

just for show SETB flag just for

show LOOP1 CLR C Clear carry MOV

A,il ADD A,P2 increment MOV

il,A JNC LOOP1 loop until carry INC

ih increment hi byte MOV A,ih

check if zero JNZ LOOP1 XRL

P1,01H SJMP LOOP1 END

NAME FLASH PUBLIC il PUBLIC ih PROG SEGMENT COD

E CONST SEGMENT CODE VAR1 SEGMENT DATA BITVAR SEG

MENT BIT STACK SEGMENT IDATA RSEG BITVAR flag

DBIT 1 RSEG VAR1 ih DS 1 il DS

1 RSEG STACK DS 10H 16 Bytes

Stack CSEG AT 0 USING 0

Register-Bank 0 Execution starts at address 0

on power-up. JMP START

10

Compiled C

But, here is the optimized Compiled C

?C0001 XRL P1,01H CLR A MOV i,A MOV

i01H,A ?C0005 MOV R7,i01H MOV R6,i MOV

R5,P2 MOV A,R5 ADD A,i01H MOV

i01H,A CLR A ADDC A,i MOV i,A CLR

C MOV A,R7 SUBB A,i01H MOV A,R6 SUBB

A,i JC ?C0005 SJMP ?C0001

11

I/O Ports

- Input ports Hi Input impedance (like CMOS

transistor gate) - Output ports Hi drive (current source/sink)

capability (like CMOS transistor channel) - Bidirectional Ports?

- Weak Pullup Approach used in the 8051

- Configuration bits (used in other MCUs)

12

Basic Electronics

- Speaker Interface. Design a direct drive circuit

for the speakers. How much power are we

dissipating in the speaker if we stay within

current rating of chip? - How can we get more power to the speaker?

- Note to self Saturation v. Linear operation

13

Lab 2

- Design and implement Audio Amplifier interface to

8051. - Simple program (in assembly) that can generate a

controllable range of audio frequencies (like

lab1, but different range of frequencies and use

interrupts instead of busy waiting). - Use interrupts to generate the pulse trains

- Any algorithm suggestions? Lets keep it simple!!

- Lab write-up

- Characteristics of your speaker min max tone

frequency, audibility (loadness) v. frequency,

etc. Anything else you notice - Are your drive transistors operating in linear or

saturation mode? How can you tell? - Resource Utilization Analysis

- of time in ISR (can you minimize this?)

- Worst case stack size

14

Embedded Hardware

- Microcontrollers

- Smallest PIC 8-Pin (8-bit) PIC 8-pin

Microcontroller - Middle 6805 (8 bit) Example Flash Based 8051

- Many 16-bit DSP Microcontrollers

- HW support for MAC, Filter Algorithms

- High End StrongArm (32 bit) Intel

- Compare to pentium

- External memory

- Data Address Multiplexing

- Memory Mapped I/O

- Device Interfaces

- Resistive Sensors (Strain, Temp, Gas, etc.)

- Motion sensors (accelerometer)

- Valve

- Motor (Stepper, DC, Servo)\

- Speaker

- LCD Display

- LED

- Latches