Gestione delle subroutine - PowerPoint PPT Presentation

Title:

Gestione delle subroutine

Description:

Esercizio Esame Un processore PD32 interfacciato a due periferiche di input A e B, e ad un DMAC il quale puo gestire trasferimento di dati da B verso la memoria. – PowerPoint PPT presentation

Number of Views:43

Avg rating:3.0/5.0

Title: Gestione delle subroutine

1

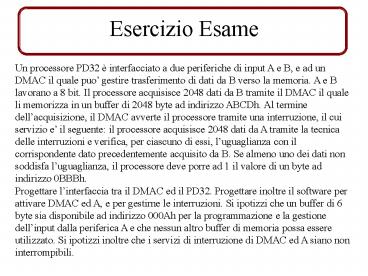

Esercizio Esame

Un processore PD32 è interfacciato a due

periferiche di input A e B, e ad un DMAC il quale

puo gestire trasferimento di dati da B verso la

memoria. A e B lavorano a 8 bit. Il processore

acquisisce 2048 dati da B tramite il DMAC il

quale li memorizza in un buffer di 2048 byte ad

indirizzo ABCDh. Al termine dellacquisizione, il

DMAC avverte il processore tramite una

interruzione, il cui servizio e il seguente il

processore acquisisce 2048 dati da A tramite la

tecnica delle interruzioni e verifica, per

ciascuno di essi, luguaglianza con il

corrispondente dato precedentemente acquisito da

B. Se almeno uno dei dati non soddisfa

luguaglianza, il processore deve porre ad 1 il

valore di un byte ad indirizzo 0BBBh. Progettare

linterfaccia tra il DMAC ed il PD32. Progettare

inoltre il software per attivare DMAC ed A, e per

gestirne le interruzioni. Si ipotizzi che un

buffer di 6 byte sia disponibile ad indirizzo

000Ah per la programmazione e la gestione

dellinput dalla periferica A e che nessun altro

buffer di memoria possa essere utilizzato. Si

ipotizzi inoltre che i servizi di interruzione di

DMAC ed A siano non interrompibili.

2

Logica dellinterfaccia del DMAC per le

interruzioni

IRQ

CPU

I/O AB

I/O DB

I/O CB

START

CLEAR

IACKIN

IRQ

IVN

STARTD

Decoder

O.C.

SELECT

COMPLETE

SCO DMAC

STARTDEV

IACKOUT

3

AB

PD32

DB

MEMORIA

CB

8 bit

I/O WR

INC

CAR

8 bit

LD

REG

REG

SELECT

DECR

MRD

WC

I/O WR

TC

NEXT DATO

Q

MBR

SCO DMAC

SCO DEV_B

MBR F/F

IRQ

I/O AB

O.C.

DATO PRONTO

MBG

I/O DB

I/O CB

STATUS F/F

4

Interfaccia DEV_A

CPU

IRQ

I/O AB

I/O DB

I/O CB

IRQ

START

IORD

CLEAR

IACKIN

IVN

Dec

SELECT

OR

REG

COMPLETE

SCA

SCO

STARTDEV

IACKOUT

5

org 400h INIZIO PROGRAMMA dev_a equ 0h

indirizzo device A dev_b equ 1h indirizzo

device B dmac equ 2h indirizzo

dmac CAR equ 3h indirizzo dmac WC

equ 4h indirizzo dmac risultato equ

0BBBh indirizzo byte riservato

alluscita buffer_lavoro equ 000Ah indirizzo 6

byte riservato alla logica del programma code j

sr init seti abilita PD32 ad accettare

interruzioni main ... jmp main init outl

2048, WC outl ABCDh, CAR start dmac ret

6

DRIVER DMAC driver 0, 600h push r0 salva

contenuto dei registri sporcati nella

routine clear dmac elimino la causa

dellinterruzione sul dmac movl ABCDh,

buffer_lavoro movl buffer_lavoro, r0 addl 4,

r0 movw 0, (r0) start dev_a pop r0 rti

7

DRIVER dev_A driver 1, 700h push r0, r1,

r2, r3 salva contenuto dei registri sporcati

nella routine inb dev_A, r0 acquisisco il dato

dalla periferica dev_A movl 000Ah,

r1 acquisisco lindirizzo corrente per il

controllo cmpb (r1), ro r0- valore

corrispondente in memoria JNZ set_flag aggiorna

addl 4, r1 movl r1, 000Ah aggiorno

lindirizzo che punterà al prossimo dato da

controllare movl 000Ah, r2 addl 4, r2 movw

(r2), r3 sposto in r3 il valore del

contatore addw 1,r3 aggiorno il

contatore cmpw 2048, r3 jz interrompi_esecuzion

e start dev_A jmp fine set_flag movb 1,

0BBBh jmp aggiorna interrompi_esecuzione clear

dev_A fine RTI