Buffering PowerPoint PPT Presentation

Title: Buffering

1

Buffering

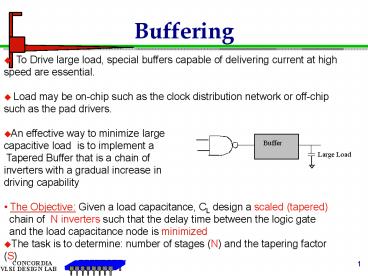

- To Drive large load, special buffers capable of

delivering current at high speed are essential. - Load may be on-chip such as the clock

distribution network or off-chip such as the pad

drivers. - An effective way to minimize large

- capacitive load is to implement a

- Tapered Buffer that is a chain of

- inverters with a gradual increase in

- driving capability

- The Objective Given a load capacitance, CL

design a scaled (tapered) - chain of N inverters such that the delay time

between the logic gate - and the load capacitance node is minimized

- The task is to determine number of stages (N)

and the tapering factor (S)

2

OUTPUT Pad and Driver

3

CLOCK DRIVER

4

Buffering

S scaling or tapering factor CL SN1 Cg

All inverters have identical delay of to

delay of the first stage (load CdCg)

5

Buffering

If the diffusion capacitance Cd is neglected,

then S e 2.7

6

Layout of a standard inverter

7

Layout of Large Device

- Drain-Source Area

- Delay of Gate

8

Layout of a Buffer

(a) small transistors in parallel

(b) circular transistors

Prentice Hall/Rabaey

9

Large Transistor Layout

Increase of Contacts

10

Output Drivers

Standard CMOS Driver Open Drain/Source Driver

Single Transistors Tri-state Driver Bi-directio

nal Circuit

11

Output Drivers

Bonding Pad

GND

100 mm

Out

Out

VDD

In

GND

Prentice Hall/Rabaey

12

Tri-state Driver

- Tri-state or High impedance

- Used to drive internal or external busses

- Two inputs

- Data In and Enable

- Various signal assertions

- Two types

- C2MOS

- CMOS with Control Logic

C2MOS

13

Tri-state Driver

V

Control logic could be modified to obtain

Inversion/non-inversion Active low/high

Enable For large load, pre-drivers are required

DD

En

PAD

Out

En

In

14

Latch-up on CMOS

Inherent in bulk CMOS processes are parasitic

bipolar transistors forming p/n /p /n path

between VDD and VSS The four layer path is

equivalent to SCR which when triggered can cause

self sustaining latch-up between power supplies

resulting in total or local destruction.

VDD

VDD

VSS

n

p p

n n p

Drain of

Rs

NMOS

T1

Rw

T2

T1

T2

P-well

Drain of

Rs

PMOS

Rw

n-substrate

Vss

15

Latch-up Analysis

- If VAgtVDD0.6, T1 will be turned ON

- Ic1 causes a voltage drop across Rw

- If V(Rw) gt 0.6V V, T2 will be turned ON,

- this forces Ic2 to be supplied by VDD through

- n substrate contact, then the bulk to p-well.

- Increase in voltage across Rs causes and in

- increase in Ic1, hence sustaining SCR action.

- The same action will take place when

- VBlt -0.6V

- Hence to prevent latch-up, limit the output

voltage - -0.6lt Vout lt

VDD0.6V

IE1

Rs

VA

IB1

IC1

IC1

T2

IB2

VB

Rw

IE1

16

Latch-up Trigger

- Factors which trigger latch-up

- transmission line reflections or ringing

- voltage drop on the VDD bus

- hot plug in of unpowered circuit board

- electrostatic discharge

- sudden transient on power and ground busses

- leakage current across the junction

- radiation x-ray, cosmic

17

Latch-up Prevention

1. Layout techniques Incorporate collectors

for latch-up current Create diffused n and p

guard rings that surround active devices

These collectors can sink the current but are

incapable of sustaining the latch-up

mechanism once the cause is removed

guard ring

n

n

n

n

p

p

p

p

GND

18

Input protection

- Electrostatic discharge can take place through

transfer of charges from the human body to the

device. - Human body can carry up to 8000V.

- Discharge can happen within hundreds of

nanoseconds. - Critical field for SiO2 is about 7X106 V/cm.

- For 0.5u CMOS process the gate oxide can

withstand around 8V - Some protection technique is required with

minimum impact on performance

1.5K?

1M?

Vesd

DUT

100pF

Human Body model

19

Input PAD

20

Protection Circuitry Principles

Avalanche

Punch Through

21

ESD Structures

Basic technique is to include series resistance

and two clamping diodes. The resistance R is to

limit the current and to slow down the high

voltage transitions. R could be polysilicon or

diffusion resistance Diffusion resistance could

be part of the diode structure Typical values of

R 500 to 1k

VDD

R

PAD

22

Protection Circuitry

Based on gate modulated junction breakdown

23

Protection Circuitry

24

Layout of ESD Structure

This structure uses transistors as clamping diodes

25

Layout of ESD Structure

26

VDD

27

Structure of a P Diode

VDD

N Guard

M1

N Sub

P

Input

OUTPUT

28

Another ESD Structure

VDD

R1

R2

PAD

Thick FOX MOS Transistor

29

Bi-direct PAD

V

DD

Pre-drivers

ESD Protection

Input Buffer

IN

PAD

Control Logic

EN

30

(No Transcript)

31

2D vs. 2.5D vs. 3D ICs 101 By Clive Maxfield

4/8/2012 1208 PM EDT

Birds-eye view of circuit board witha

System-on-Chip (SoC) device

Birds-eye view of circuit board with

individually packaged chips

Birds-eye view of circuit board with a

System-in-Package (SiP) device

Birds-eye view of circuit board with a

System-in-Package (SiP) device

32

3D Structures 2D vs. 2.5D vs. 3D ICs 101

By Clive Maxfield 4/8/2012 1208 PM EDT

Connecting dice using wires running down the

sides 3D stack

A simple form of 3D IC/SiP

A more complex True 3D IC/SiP

A simple True 3D IC/SiP

33

Thank you !