Evolution of Intel CPU PowerPoint PPT Presentation

1 / 32

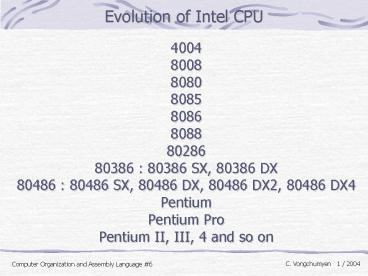

Title: Evolution of Intel CPU

1

Evolution of Intel CPU

4004 8008 8080 8085 8086 8088 80286 80386

80386 SX, 80386 DX 80486 80486 SX, 80486 DX,

80486 DX2, 80486 DX4 Pentium Pentium Pro

Pentium II, III, 4 and so on

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

2

Speed Test of Intel CPU

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

3

Microcomputer

Input

CPU

Output

Memory

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

4

CPU Task

- ????????????????????????????? Memory ??? I/O

- ?????????????????????????????????????

- ????????? Flow ???????????

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

5

2 3

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

6

2 3

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

7

2 3

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

8

CPU VS. Human

- Complexity of processing

- Speed

- Correctness

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

9

CPU

Central Processing Unit

ALU

Arithmetic Logic Unit

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

10

ALU

Note Comparators store result in Status

Register ( Flag )

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

11

Zero Address Instruction

Get 2 data from stack to add

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

12

Zero Address Instruction

Store result back to stack

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

13

Single Address Instruction

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

14

Single Address Instruction

Load and Store architecture

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

15

Next Step of CPU

After add BX, CX, DX Data bus Internal and

External

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

16

Next Step of CPU

After add BP, SI, DI New type of bus address bus

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

17

CU Control Unit

ROM

ALU

CU

Microprogram Microcode

An other type of CU is Hardwire

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

18

Subsequence of Instruction

- Add AX, BX

- AX to Buffer Register in ALU

- BX to Buffer Register in ALU

- Perform Add operation

- Store result back to AX

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

19

Add Instruction Decoder,Control Unit and

Control Bus

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

20

CPU Component

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

21

CU Subsequence (mov a, 80h)

- Program Counter ???????????? 0 ??????????????????

CU ???????????????????? Address Bus - Address Bus ??????????? 0000h ???????????????????

Address ?????????????? 0000h - CU ????????? Read ??????????????????????????

Control Bus - ????????????????????????????????? Read ???

????????????????????????????? 0000h ????? - CU ??????? Instruction Decoder ???????????? Data

Bus ?????????? - Instruction Decoder ?????????????? CU

??????????????????? Microcode ?????? Sequencer

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

22

CU Subsequence

- Instruction Decoder ?????????????? PC

??????????????????????????????? - CU ???????????????? Sequencer ???? ?????????? PC

?????????????????? (?????????? 0001h) - CU ????????? Read ?????

- ????????????????????????????????? Read

???????????????????? (80h) ????????? Data Bus - CU ??????? Accumulator ????????????????

- CU ??????? PC ????????????????????????? ????

0002h

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

23

8086

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

24

Upgrade CPU

- Prefetch Queue

- Problem found when jump

- Cache ( SRAM )

- L1 Cache ( Unify and Separate )

- Instruction Cache ( Pentium )

- Data Cache

- L2 Cache

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

25

Cache

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

26

Upgrade EU

Pipeline

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

27

Pipeline

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

28

8086 Instruction time

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

29

80286 Instruction time

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

30

Pipeline Hazard

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

31

Solution of Pipeline Hazard

- Optimize code by compiler

- Superscalar technique

- Branch prediction

- Prefetch Queue

- Pipeline

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6

32

Branch Prediction

- Prefetch queue

- fetch both instruction

- Pipeline

- Statistic

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 6