Mips PowerPoint PPT Presentations

All Time

Recommended

Mini-MIPS From Weste/Harris CMOS VLSI Design

| PowerPoint PPT presentation | free to download

PIPELINE Pipeline no MIPS Implementa o do Pipeline O que facilita: Todas as instru es com mesmo comprimento Somente poucos formatos de instru es Os operandos ...

| PowerPoint PPT presentation | free to download

MIPS coding. SPIM. Some links can be found such as: ... Here by comparing arrays and pointers in MIPS assembly we can have a much better ... Comparing Two Versions ...

| PowerPoint PPT presentation | free to download

Title: Interrupts & Input/output Author: S. Dandamudi Last modified by: Sivarama Dandamudi Created Date: 11/24/1998 12:49:00 AM Document presentation format

| PowerPoint PPT presentation | free to download

MIPS History MIPS is a computer family R2000/R3000 (32-bit); R4000/4400 (64-bit); R8000; R10000 (64-bit) etc. MIPS originated as a Stanford research project under the ...

| PowerPoint PPT presentation | free to download

Now it is straightforward to translate the C program into MIPS assembly ... PC-relative addressing. The offset of conditional branch instructions is relative to PC 4 ...

| PowerPoint PPT presentation | free to download

COE 308 MIPS Instructions MIPS Instructions in MIPS Reduced Instruction Set 3 Operands per operation: 2 sources and 1 destination Most instructions are of the form ...

| PowerPoint PPT presentation | free to download

How to extract op code from an instruction? We need logical operations ... How to Extract Opcode and Other Fields. We want to use the minimum number of instructions ...

| PowerPoint PPT presentation | free to download

Note a program (including data (variables)) is loaded from memory ... Store 0x87654321 at address 0x0000, byte-addressable. CDA3100. 6. Example of Endianness ...

| PowerPoint PPT presentation | free to download

Your task: build lexer and parser. using ML-Lex and Yacc. Today: Quick overview of the MIPS instruction set. We're going to be compiling to MIPS assembly language. ...

| PowerPoint PPT presentation | free to view

AddressOut and WriteDataOut are output ports. Reset clears regfile and all registers ... Send data to each stage through previous stages ...

| PowerPoint PPT presentation | free to download

Overflow (and underflow also for floating numbers) happens when a number is ... If a number is larger than 127, it will cause overflow also ...

| PowerPoint PPT presentation | free to download

Given: AST for a small, C-like ... Quick overview of the MIPS instruction set. ... Unconditional Jumps: j imm26 ; pc := (imm26 2) jr $rs ; pc := $rs ...

| PowerPoint PPT presentation | free to view

MIPS assembly Exercise 2 How to implement this with only the instructions we learnt? if ($t1 $t2) $t0 = $t1; else $t0 = $t2; Exercise 2 # if ($t1 $t2) $t0 ...

| PowerPoint PPT presentation | free to download

MIPS Assembly Language I

| PowerPoint PPT presentation | free to download

MIPS instructions

| PowerPoint PPT presentation | free to download

CDA 3101 Discussion Section 03 MIPS Assembly Language Programming (2) * Basic Instructions Manipulate data: ADD SUB MUL DIV AND OR XOR ADDI SLL

| PowerPoint PPT presentation | free to view

The Merit-based Incentive Payment System (MIPS) is new payment reimbursement technique. Read more about MIPS and how it functions for your medical practice.

| PowerPoint PPT presentation | free to download

In J-type instructions, the jump address is formed by upper 4 bits of the ... Execute a jal instruction, which jumps to the callee's first instruction and ...

| PowerPoint PPT presentation | free to download

MIPS Assembler Programming Prof. Sirer CS 316 Cornell University

| PowerPoint PPT presentation | free to download

Modern processors use this design philosophy. PowerPC, MIPS, SPARC, Intel Itanium ... No precise definition. We can identify some common characteristics. 2005 ...

| PowerPoint PPT presentation | free to view

Title: Interrupts & Input/output Author: S. Dandamudi Last modified by: Sivarama Dandamudi Created Date: 11/24/1998 12:49:00 AM Document presentation format

| PowerPoint PPT presentation | free to download

Based on POWER architecture. 1991, Apple-IBM-Motorola (AIM) alliance ... Xbox 360 Elite PPC 3 cores 3.2 GHz. Wii - 729MHz Broadway. Game Cube - 485MHZ Gekko ...

| PowerPoint PPT presentation | free to view

CDA 3101 Discussion Section 04 MIPS Assembly Language Programming Problem1 int chico[10] = {1, 2, 3, 4, 5, 6, 7, 8, 9, 10}; int sum; void main() { int t1 = 0; int ...

| PowerPoint PPT presentation | free to download

Title: Slide 1 Author: Taeweon Suh Last modified by: Taeweon Suh Created Date: 8/14/2004 10:46:03 PM Document presentation format: On-screen Show (4:3)

| PowerPoint PPT presentation | free to download

MIPS Assembly Tutorial. Types of Instructions. There are 3 main types of assembly instructions ... Translating MIPS Assm Language to Machine Language ...

| PowerPoint PPT presentation | free to download

... 80186 not used in PCs (used for embedded systems) 80386 extends architecture to 32-bit, makes it nearly a general-purpose machine. Throughout history, ...

| PowerPoint PPT presentation | free to download

College of Computer Sciences and Engineering. King Fahd University of Petroleum and Minerals ... Halfword address should be a multiple of 2 .ALIGN n directive ...

| PowerPoint PPT presentation | free to download

... . if/else do/while while Introduction to SPIM Now let s take a quick look at the xspim program and try to write and run the Fibonacci numbers program.

| PowerPoint PPT presentation | free to download

Booth s Algorithm is an elegant way to multiply signed numbers using the same hardware as before and save cycles: Can handle multiple bits at a time.

| PowerPoint PPT presentation | free to download

I format - Uses two register operands and an address/immediate value ... Indexed Address - Adds address field and register value and uses this as address ...

| PowerPoint PPT presentation | free to download

To be used with S. Dandamudi, 'Introduction to Assembly Language ... Chapter 13: Page 3. Instruction Format. load, arithmetic/logical. with immediate operands ...

| PowerPoint PPT presentation | free to view

Check the newly updated Centers for Medicare & Medicaid Services (CMS) online tool to see whether you must participate in MIPS. All you need is your National Provider Identifier (NPI) to learn if you’re required to participate in 2019. CMS will not mail MIPS status letters to group practices in 2019, so it’s important to check the lookup tool to determine your status.

| PowerPoint PPT presentation | free to download

Let's use this lecture to start to develop a simple TV controller together. ... Once it becomes 0, turn the TV off immediately and print out 'Power Off Due To ...

| PowerPoint PPT presentation | free to download

MIPS Assembly Language Chapter 15 S. Dandamudi Outline MIPS architecture Registers Addressing modes MIPS instruction set Instruction format Data transfer instructions ...

| PowerPoint PPT presentation | free to download

MIPS Architecture Multiply/Divide Functions & Floating Point Chapter 4 By N. Guydosh 2/18/04 Multiplication Element for MIPS First hardware algorithm is a take-off on ...

| PowerPoint PPT presentation | free to download

Instruction Decode Phase 1. The op-code parts of the instruction is examined ... The previous operations Fetch and Decode are. common to operation several types ...

| PowerPoint PPT presentation | free to view

2. MIPS. Assembly Language Programming. CDA 3101 Discussion Section 03. Outline ... Click this menu item to change settings for the emulator. ...

| PowerPoint PPT presentation | free to view

CSE 675.02: Introduction to Computer Architecture Instruction Set Architecture of MIPS Processor Presentation B Slides by Gojko Babi

| PowerPoint PPT presentation | free to download

Comments begin with #. Everything from # to the end of the line is ignored. Identifiers are a sequence of alphanumeric characters, underbars (_), and dots (.) that do ...

| PowerPoint PPT presentation | free to download

MIPS Assembly Language Chapter 13 S. Dandamudi Outline MIPS instruction set Instruction format Data transfer instructions Arithmetic instructions Logical/shift/rotate ...

| PowerPoint PPT presentation | free to download

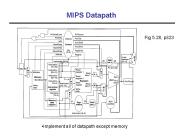

CSE 675.02: Introduction to Computer Architecture Designing MIPS Processor (Single-Cycle) Presentation G Slides by Gojko Babi We're now ready to look at an ...

| PowerPoint PPT presentation | free to download

Lecture 3: MIPS Instruction Set ... 6 bits 5 bits 5 bits 16 bits opcode rs rt constant * Logical Operations Logical ops C operators Java operators ...

| PowerPoint PPT presentation | free to download

MIPS Assembly Tutorial Types of Instructions There are 3 main types of assembly instructions Arithmetic - add, sub, mul, shifts, and, or, etc. Load/store Conditional ...

| PowerPoint PPT presentation | free to download

... are added together LW Example Data in Memory All variables/data are stored in memory You will need to do this in your assembler ... MIPS - Machine Language ...

| PowerPoint PPT presentation | free to download

MIPS Machine Assembly Language

| PowerPoint PPT presentation | free to download

Title: PowerPoint Presentation Last modified by: lenovo Created Date: 1/1/1601 12:00:00 AM Document presentation format: (4:3) Other titles

| PowerPoint PPT presentation | free to download

Title: A single-cycle MIPS processor Subject: CS232 @ UIUC Author: Howard Huang Description 2001-2003 Howard Huang Last modified by: kumar Created Date

| PowerPoint PPT presentation | free to download

Sample Undergraduate Lecture: MIPS Instruction Set Architecture Jason D. Bakos Optics/Microelectronics Lab Department of Computer Science University of Pittsburgh

| PowerPoint PPT presentation | free to view

Sample Undergraduate Lecture: MIPS Instruction Set Architecture Jason D. Bakos Optics/Microelectronics Lab Department of Computer Science University of Pittsburgh

| PowerPoint PPT presentation | free to view

We will be reusing functional units. ALU used to compute address and to increment PC ... used for Vax 780 an astonishing 400K of memory! Lots of encoding: ...

| PowerPoint PPT presentation | free to download

... word generally does not matter, except when casting between integral data types ... Such casting is typically required when sending data from one host to another ...

| PowerPoint PPT presentation | free to download

Title: PowerPoint Presentation Author: Rajeev Balasubramonian Last modified by: Rajeev Balasubramonian Created Date: 9/20/2002 6:19:18 PM Document presentation format

| PowerPoint PPT presentation | free to download