Gate-Level Test Generation Using Spectral Methods at Register-Transfer Level PowerPoint PPT Presentation

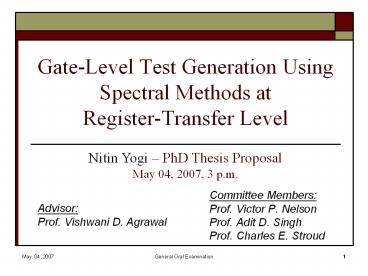

Title: Gate-Level Test Generation Using Spectral Methods at Register-Transfer Level

1

Gate-Level Test Generation Using Spectral Methods

at Register-Transfer Level

Nitin Yogi PhD Thesis Proposal May 04, 2007, 3

p.m.

- Committee Members

- Prof. Victor P. Nelson

- Prof. Adit D. Singh

- Prof. Charles E. Stroud

Advisor Prof. Vishwani D. Agrawal

2

Outline

- Introduction

- Background

- Spectral Register Transfer Level (RTL) test

generation - RTL Design for Testability (DFT)

- Results

- Future Work

- Conclusion

3

1 - Introduction

- Test generation challenges

- Test generation methods

- Problem definition

4

1.1 Test Generation Challenges

- Two main challenges

- Reducing test generation complexity

- Majority circuits sequential in nature

- Rise in design complexity

- Good quality test vectors

- High fault coverage

- Low yield loss

5

1.2 Test Generation Methods

- Scan-Based Test Generation

- Sequential Test Generation

- Register-Transfer Level (RTL) Test Generation

- Pseudo Functional Test Generation

6

1.2.1 Scan-Based Test Generation

CombinationalLogic

Circuit Outputs

Circuit Inputs

Scan Output

Functional

FF

FF

Scan FF

FF

Scan

Scan chain

Scan Input

7

1.2.1 Scan-Based Test Generation

- Advantages

- Reduced test generation complexity

- Combinational test generation

- High fault coverage

- Disadvantages

- Area overhead ( 5 10)Timing overhead ( 5

10) - Non-functional tests

- Long test times

- Issues from high test power

- Voltage droop

- Ground bounce

- Issues with at-speed scan tests

- False and multi-cycle paths

8

1.2.2 Sequential Test Generation

- Non-scan test generation

- Advantages

- Functional vectors

- Short test times

- No test power issues

- Ability to generate at-speed tests

- Disadvantages

- High test generation complexity

9

1.2.3 RTL Test Generation

- Earlier Work Jha et.al.,Hayes et. al.,Goloubeva

et. al. - Advantages

- Low test generation complexity

- Less amount of information to process

- Early detection of testability issues

- Synthesis independent

- Disadvantages

- Main issues

- Closing gap between RTL and gate-level coverage

- High engineering effort

- No established method

10

1.2.4 Pseudo Functional Test Generation

- Weighted random vectors (Brglez et. al.)

- Test vectors generated with certain probabilities

of being logic 0 or 1 - PROPTEST (Guo et. al.)

- Property based test generation

- Probabilities, holding, perturbation

- Spectral methods (Giani et. al., Khan et. al.)

- Test generation using spectral properties

- Retrieve spectral properties

- Generate new vectors with those properties

11

1.3 Problem Definition

- Summary of goals

- Generate functional test vectors

- Sequential test generation

- Low test generation complexity

- RTL test generation

- Convenient test generation method

- Spectral methods

- Hence the problem is

- To generate function vectors using sequential

test generation by using spectral methods at RTL

12

Outline

- Introduction

- Background

- Spectral Register Transfer Level (RTL) test

generation - RTL Design for Testability (DFT)

- Results

- Future Work

- Conclusion

13

2 Background

- Spectral analysis for test generation

- Walsh functions and Hadamard matrix

14

2.1 Spectral Analysis for Test Generation

- Spectral analysis Interpret information in

frequency domain - Test generation

- Good quality test vectors exhibit certain

spectral characteristics - Goals

- Determine relevant spectral characteristics

- Generate vectors with those characteristics

15

2.2 Walsh functions and Hadamard matrix

- Walsh functions a complete orthogonal set of

basis functions that can represent any arbitrary

bit-stream. - Walsh functions form the rows of a Hadamard

matrix.

w0

w1

w2

1 1 1 1 1 1 1 1 1 -1 1 -1 1 -1 1 -1 1

1 -1 -1 1 1 -1 -1 1 -1 -1 1 1 -1 -1 1 1 1

1 1 -1 -1 -1 -1 1 -1 1 -1 -1 1 -1 1 1 1 -1

-1 -1 -1 1 1 1 -1 -1 1 -1 1 1 -1

H8

w3

w4

Walsh functions (order 8)

w5

w6

w7

time

Example of Hadamard matrix of order 8

Move to next section

16

Outline

- Introduction

- Background

- Spectral Register Transfer Level (RTL) test

generation - RTL Design for Testability (DFT)

- Results

- Future Work

- Conclusion

17

3 Spectral RTL Test Generation

- Spectral characterization

- Spectral vector generation

- Test set minimization

18

3.1 Spectral Characterization

- Purpose Determine relevant spectral

characteristics - Premise Vectors detecting RTL faults exhibit

important spectral characteristics - Steps

- RTL fault modeling and test generation

- Spectral analysis

19

3.1.1 RTL Fault Modeling

CombinationalLogic

Inputs

Outputs

RTL fault sites

FF

FF

A circuit is an interconnect of several RTL

modules.

20

3.1.2 Spectral Analysis

Input 1 Input 2 . . .

Vector 1 Vector 2 . . .

Bit-stream

0 to -1

Bit-stream of Input 2

21

3.1.2 Spectral Analysis (cont.)

Bit stream to analyze

Correlating with Walsh functions by multiplying

with Hadamard matrix.

Bit stream

Spectral coeffs.

Hadamard Matrix H(3)

Essential component (others regarded noise)

22

Power Spectrum Ready Signal

PARWAN Processor Circuit

Examples of Essential components

Examples of Noise components

Normalized Power

Noise level(1/128)

Spectral Coefficients

23

Power Spectrum A Random Signal

Normalized Power

Noise level(1/128)

Spectral Coefficients

24

3.2 Spectral Vector Generation

Perturbation

Spectral components

Generation of new bit-stream by multiplying with

Hadamard matrix

Essential component retained noise components

randomly perturbed

New bit stream

Sign function

-1 to 0

Bits changed

25

3.3 Test Set Minimization

- Fault simulation of new sequences

- Set of perturbation vector sequences V1, V2, ..

, VM are generated. - Vector sequences are fault simulated and faults

detected by each is obtained. - Minimization problem

- Find minimum set of vector sequences covering all

the detected faults. - Minimize CountV1, ,VM to obtain compressed

seq. V1, ,VC Fault CoverageV1, ,VC

Fault CoverageV1, ,VM - Compaction problem formulated as an Integer

Linear Program (ILP) .

P. Drineas and Y. Makris, Independent Test

Sequence Compaction through Integer Programming,"

Proc. ICCD03, pp. 380-386.

26

3.3.1 ILP test minimization

- Set of integer 0,1 variables tj one for

each vector sequence - tj 0 drop sequence tj 1 select sequence

- Set of constraints ck one for each fault

- Example for kth fault detected by vector

sequences u, v and w ck tu tv tw 1 - Objective function

- Minimize ? tj j 1 to N

27

3.3.2 Hybrid LP ILP

- Approximate solution to ILP (Relaxed LP,

Rounding) - Algorithm

- 1. All variables redefined as real 0,1 real

variables(LP model) - 2. Loop

- 1. Solve LP

- 2. Round variables to add constraints

- 1. Round to 0 if ( 0.0 lt variables 0.1)

- 2. Round to 1 if ( 0.9 variables lt 1.0)

- 3. Exit loop if no variables are rounded

- 3. Reconvert variables to 0,1 integers and

solve ILP

Kantipudi, K.R. Agrawal, V.D, A Reduced

Complexity Algorithm for Minimizing N-Detect

Tests, 20th International Conference on VLSI

Design, 2007

28

Outline

- Introduction

- Background

- Spectral Register Transfer Level (RTL) test

generation - RTL Design for Testability (DFT)

- Results

- Future Work

- Conclusion

29

4 RTL Design for Testability

- Goals of DFT

- Improve fault coverage

- XOR tree as DFT

- Low area overhead

- Low performance penalty

- Does not change state machine

- Hard-to-detect RTL faults used for observation

test points

XOR tree

To test output

Hard-to-detect RTL faults

30

Outline

- Introduction

- Background

- Spectral Register Transfer Level (RTL) test

generation - RTL Design for Testability (DFT)

- Results

- Future Work

- Conclusion

31

5 Results

- Experimental Circuits

- Spectral RTL test generation

- Stuck-at faults

- Transition delay faults

32

5.1 Experimental Circuits

Circuit benchmark PIs POs FFs

b01 ITC99 2 2 5

b09 ITC99 1 1 28

b11 ITC99 7 6 31

b14 ITC99 34 54 239

s1488 ISCAS89 8 19 6

s5378 ISCAS89 36 49 179

s9234 ISCAS89 37 39 211

s35932 ISCAS89 36 320 1728

PARWAN processor 11 23 53

- Experimental Circuits

- 4 ITC99 high level RTL circuits

- 4 ISCAS89 circuits.

- PARWAN processor

- Commercial sequential ATPG tool Mentor Graphics

FlexTest for test generation and fault

simulation. - Results obtained on Sun Ultra 5 machines with

256MB RAM.

Z. Navabi, VHDL Analysis and Modeling of

Digital Systems, McGraw-Hill, 1993.

33

5.2.1 ATPG for stuck-at faults

34

PARWAN Processor

Z. Navabi, VHDL Analysis and Modeling of

Digital Systems, McGraw-Hill, 1993.

35

Results Test Generation

Circuit name gate-level faults RTL-ATPG spectral tests RTL-ATPG spectral tests RTL-ATPG spectral tests FlexTest Gate-level ATPG FlexTest Gate-level ATPG FlexTest Gate-level ATPG Random inputs Random inputs

Circuit name gate-level faults Cov. () No. of vectors CPU (secs) Cov. () No. of vectors CPU (secs) No. of vectors Cov ()

b09-A 882 84.68 640 730 84.56 436 384 3840 11.71

b09-D 1048 84.21 768 815 78.82 555 575 7680 6.09

b11-A 2380 88.84 768 737 84.62 468 1866 3840 45.29

b11-D 3070 89.25 1024 987 86.16 365 3076 3840 41.42

b14 25894 85.09 6656 5436 68.78 500 6574 12800 74.61

s1488 4184 95.65 512 103 98.42 470 131 1600 67.47

s5378 15584 76.49 2432 2088 76.79 835 4439 3840 67.10

s5378 15944 73.59 1399 718 73.31 332 22567 2880 62.77

s35932 103204 95.70 256 1801 95.99 744 3192 320 50.70

PARWAN 5380 89.11 1344 1006 87.11 718 3626 6400 76.63

Reset input added.

Sun Ultra 5, 256MB RAM

36

Results Test Generation and RTL DFT

Circuit RTL Spectral ATPG RTL Spectral ATPG RTL Spectral ATPG Gate-level ATPG (FlexTest) Gate-level ATPG (FlexTest) Gate-level ATPG (FlexTest) Random vecs. Random vecs.

Circuit Cov. () No. of vecs. CPU (secs) Cov. () No. of vecs. CPU (secs) Cov. () No. of vecs.

Parwan 98.23 2327 2442 93.40 1403 26430 80.95 2814

Parwan (with DFT) 98.77 1966 2442 95.78 1619 20408 87.09 2948

Sun Ultra 5, 256MB RAM

37

5.2.2 ATPG for transition faults

38

Results Test Generation

ATPG used Version of PARWAN circuit CPU secs. No. of vectors Stuck-at fault cov. () Transition fault cov. ()

RTL-spectral for transition faults Original 6428 6700 97.60 81.85

RTL-spectral for transition faults DFT for t-f 6428 5120 98.25 85.94

Gate-level FlexTest for transition faults Original 43574 1318 92.44 73.79

Gate-level FlexTest for transition faults DFT for t-f 40119 1444 96.29 81.90

Random vectors Original 51200 82.28 58.67

Random vectors DFT for s-a-f 51200 86.20 65.82

s-a-f stuck-at faults t-f

transition faults

Sun Ultra 5, 256MB RAM

39

Outline

- Introduction

- Background

- Spectral Register Transfer Level (RTL) test

generation - RTL Design for Testability (DFT)

- Results

- Future Work

- Conclusion

40

6 Future Work

- Fourier Analysis of Digital Waveforms

- Spectral BIST

41

6.1 Fourier Analysis of Digital Waveforms

- Fourier Transform converts signals to frequency

domain - Digital bit-streams can be perceived as sampled

analog signals - Important properties (not exhibited by Walsh

functions) - Frequency decomposition using Fourier transform

is invariant to phase or circular time-shift - Multiplication Convolution

(frequency domain) (time domain) - Other advantages of Fourier Transform over Walsh

- Established methods for noise analysis

- Methods to find Power Spectral Density (PSD)

42

6.2.1 Built-In Self Test

- Built-In Self Test (BIST)

- Hardware inserted to

- Generate test vectors

- Capture responses of CUT

- Flag CUT good or bad

System Inputs

Test generator

Wrapper

Circuit Under Test (CUT)

Response Analyzer

CUT status

System Outputs

43

Motivation for Spectral BIST

- BIST

- Advantages

- No need of expensive Automatic Test Equipment

(ATE) - Testing during operation and maintenance

- Supports system level test

- Supports at-speed testing

- And many more

- Disadvantages

- Low coverage test vectors

- Area / timing overhead

- Problem is

- To design a test pattern generator with spectral

information that generates high coverage test

vectors

44

Fourier Transform of Test Bit-Stream

Prominent features

45

6.2.2 Spectral BIST

Test generator

Spectral Test Generator

System Inputs

Spectral Filter

Wrapper

Circuit Under Test (CUT)

Response Analyzer

CUT status

System Outputs

46

Digital Filter Design

- If y output of filter x input of filter

n time period p order of filter - Infinite Impulse Response (IIR)

- y(n) f (y(n-1), .. y(n-p), x(n), x(n-1),

x(n-p)) - Finite Impulse Response (FIR)

- y(n) f (x(n), x(n-1), x(n-p))

- IIR would require more hardware than FIR

47

Spectral Test Generator

LFSR

Spectral Test Generator

Test generator

Spectral Filter

FIR filter

48

FIR Filter Design

FIR filter

49

FIR filtering

Random bit-stream after filtering

Random bit-stream

Filter

50

How good is the filtered bit-stream ?

Original test bit-stream

Random bit-stream after filtering

51

Results - Comparison

Test Set No. of vectors No. of faults detected Total no. of faults Test cov. ()

RTL vectors 112 325 485 76.86

Flextest vectors 1410 364 485 84.09

Random vectors 65000 44 485 12.51

Filtered vectors 65000 364 485 84.09

s382

Test Set No. of vectors No. of faults detected Total no. of faults Test cov. ()

RTL vectors 103 339 639 59.21

Flextest vectors 1950 448 639 76.72

Random vectors 65000 55 639 10.75

Filtered vectors 65000 450 639 76.88

s526

52

Results Graphs

53

Results Graphs

54

Conclusion

- We have presented a new method for gate-level

test generation using spectral methods at RTL - Proposed Spectral RTL ATPG technique applied to

ITC99 and ISCAS89 benchmarks, and a processor

circuit - In most cases, Spectral RTL ATPG gave similar or

better test coverage in shorter CPU time as

compared to commercial sequential ATPG tool

FlexTest - Proposed RTL DFT technique enhanced fault

coverages

55

Conclusion Future Work

- Investigate Fourier analysis of digital

bit-streams - Compare Walsh and Fourier analysis

- Investigate their use for signature analysis

- Research on spectral test generator for BIST

- Experiment with different designs of LFSR

- Efficient design of spectral filter

56

Thank You !

- Questions ?