Asynchronous Input Example PowerPoint PPT Presentation

Title: Asynchronous Input Example

1

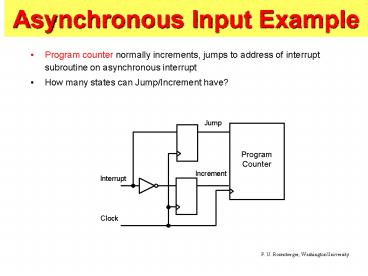

Asynchronous Input Example

- Program counter normally increments, jumps to

address of interrupt subroutine on asynchronous

interrupt - How many states can Jump/Increment have?

Jump

Program Counter

Increment

Interrupt

Clock

F. U. Rosenberger, Washington University

2

Asynchronous Input Example Revised

Jump

Program Counter

Increment

Interrupt

Clock

- Did we solve the problem? Why not?

F. U. Rosenberger, Washington University

3

Metastability

- Metastable State signal not 1 or 0 or

- oscillating for a nondeterministic length of

time - Can occur when insufficient energy is applied to

cause a latch to switch to either a 1 or 0. - Examples

- Dual processor with shared memory

- FIFO with asynchronous input and output

- Processor interrupts

- Yellow traffic light

- Two people meet in hallway

- Dog midway between two food dishes may starve

Altera Application Note 42

4

Design Approach Where Metastability Present

- Dont look for solution, there is none (dont

believe everything you read). - Bottom line - Cant guarantee correct operation

with arbitrary clock and data phase - Do design such that worst case probability of

error is acceptable - Do understand and be able to identify trouble

spots in design

F. U. Rosenberger, Washington University

5

Why Metastability is a Special Problem, Charles

E. Molnar

- Because it breaks most of the conceptual and

computatonal tools that we use from day to day

(e.g., binary or two state circuits) - It defies careful and accurate measurements

- It can produce failures that leave no discernable

evidence - It can cause failures in systems whose software

is correct and whose hardware passes all

conventional tests - It involves magnitudes of time and voltage to be

removed from our daily experience

F. U. Rosenberger, Washington University

6

Metastability in D Flip-Flops

For D Flip-Flop, caused by setup or hold-time

violations

tMET time of metastability

Altera Application Note 42

7

Analyzing Metastability

Mean Time Between Failure (MTBF) for a

synchronization flip-flop can be estimated with

the following formula where fCLOCK is the

system clock frequency fDATA is the data

transfer frequency tMET is the additional time

allowed for the flip-flop to settle C1 and C2

are device specific parameters found by plotting

the natural log of MTBF versus tMET and

performing linear regression analysis on the data

Altera Application Note 42

8

MTBF vs. TMET

Mean Time Between Failure

Altera Application Note 42

Time of metastability

9

Metastability Test Circuit

Circuit that can be used to count metastable

events

Altera Application Note 42

10

Determining TMET for a given MTBF

From test circuit we can find C2 Then we can

solve for C1 With C1 and C2 known, can find

required tMET for given clock and data rates and

required MTBF.

Altera Application Note 42

11

Application Example

Example Altera Flex 10K C1 1.01 x 10-13, C2

1.268 x 1010 For one year (3x107 seconds) and

a data frequency of 2MHz and a clock frequency of

10 MHz Small increases in tMET dramatically

affect the MTBF. A tMET delay to 1.59 ns

increases MTBF to 10 years.

Altera Application Note 42

12

Synchronizer Circuits

Example tMET is the clock period minus

the setup time and wiring delays (and

combinational logic delays if there is logic

between the flip-flops).

Metastable Output

Synchronized Output

Data

Clock