Final exam review - PowerPoint PPT Presentation

1 / 24

Title:

Final exam review

Description:

Old ways of designing digital circuits. PLD, CPLD, FPGA, ASIC. HDL, VHDL, Verilog. VHDL Tutorial. Entities. Archetectures. Simulation. VHDL elements. Identifier ... – PowerPoint PPT presentation

Number of Views:34

Avg rating:3.0/5.0

Title: Final exam review

1

Final exam review

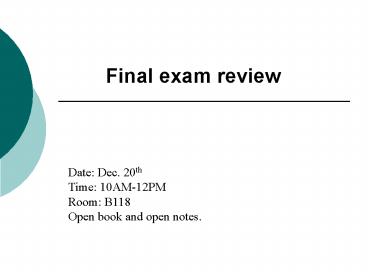

Date Dec. 20th Time 10AM-12PM Room B118 Open

book and open notes.

2

Coverage

Chapter 1- chapter 11 and Lab

3

Overview of Digital system design

- Old ways of designing digital circuits

- PLD, CPLD, FPGA, ASIC

- HDL, VHDL, Verilog

4

VHDL Tutorial

- Entities

- Archetectures

- Simulation

5

VHDL elements

- Identifier

- A,b, sum, cout

- Data objects

- signal, variable, file, constant

- Data types

- Std_logic, bit_vector, integer

- Operators

- And, or, not ,-,,/

6

VHDL elements

7

Behavioral Modeling

- Process

- sequential executed statements

- sensitivity list (hw)

- signal vs variables (hw)

- wait statement

- signal drivers

- transport and inertial delay model

- multiple processes

8

Structural Modeling

- Component declaration

- Component instantiate

- Port map()

- Connecting components using signals

9

Structural Modeling

10

Dataflow Modeling

- Concurrent signal assignment

- Block

- Guarded block

- Multiple drivers

- Resolution function

11

Primitives

- AND, or, not, xor Gates

- D flipflop, Register, Shift register

- Multiplexer, N bit adder

- Counter, comparator

- Decoder(LED), encoder

12

Primitives

- Full adder

- Decoder(LED Decoder)

- Counter

- Comparator

13

Testbench and Simulation

14

A Simple Test Bench

15

Testbench and Simulation

16

Generics

Generic map()

L

R

R

R

R

R

R

R

R

R

MB bits

E

E

E

E

E

E

E

E

E

G

G

G

G

G

G

G

G

G

h

h

h

h

h

h

h

h

h

0

1

2

3

4

5

6

7

8

1

2

1

3

1

4

5

1

1

1

1

1

MB bits

17

Subprograms and Overloading

Functions Procedures

18

The lab example

Using Bit_vector

Using integer

19

Subprogram overloading

- Distinguish between overloaded subprograms

- subprogram name

- number of actuals

- types and order of actuals

- names of formal prameters(if named association

is used) - result type(for fucntion)

20

Generate Statement

For generate If generate

21

Aliases

15

8

5

4

3

0

DATA_BUS

RESET

STATUS

RX_READY

22

Attribute

Value attributes'left 'right 'high 'low 'length

'ascending Function attributes for a type

'pos(value) 'val(value) 'succ(value) 'pred(value)

'leftof(value) rightof(value) Function

attributes for signals'event 'active

'last_event 'last_value 'last_active

23

Lab

Board setup and test skills LED 8 bit

counter VGA Round ball Audio Multiplexer using

DIP

24

Questions?

- Good Luck!